adroc_thurston

Diamond Member

10%.and 5-10% for 18A iirc

10%.and 5-10% for 18A iirc

Did you not spend any time reading the Intel roadmap? It's all been there for years in fancy power point colorful slides. They didn't use 20A because the performance trailed TSMC silicon and they were having yield issues. The backside power is unique to 18A. The power via ribbon stuff is 20A and 18A. 18 is also a denser fab as well as a shrink from 20A.Well, maybe I am wrong about 18A being renamed 20A, guess we'll have some more info leaking in the next couple of years.

It still feels one of them was a fugazi - maybe it was 20A that was just a hedge for real total disaster, and when that did not happen they called what they have reached as 18A as it was closer to it than 20A. Either way something stinks there.

Power via is backside power. The 18a process was downgraded from the initial spec but not sure if it reverted all the way back to the initial 20a spec.Did you not spend any time reading the Intel roadmap? It's all been there for years in fancy power point colorful slides. They didn't use 20A because the performance trailed TSMC silicon and they were having yield issues. The backside power is unique to 18A. The power via ribbon stuff is 20A and 18A. 18 is also a denser fab as well as a shrink from 20A.

Everything I right is long term memory and recall memory. So many people use AI or have detailed note when responding to posts. I also write posts so I can refer to myself using google searches years later.

The 14 gen stuff was garbage. We all know TSMC silicon is good stuff. Intel failed on Meteor Lake using TSMC silicon. Alder Lake was good. Intel doesn't need success on Nova Lake. They need to be able to quickly change gears and use a different process is 18A and Nova Lake are not good. Intel should really figure out how to make integrated GPU's that have performance equal to a Nvidia 4070 with motherboards that have GDDR7 slots where customers can add or change the amount of VRAM on their motherboards. This would be in addition to the standard DDR5 memory slots that have traditional been used as the vram for integrated graphics.

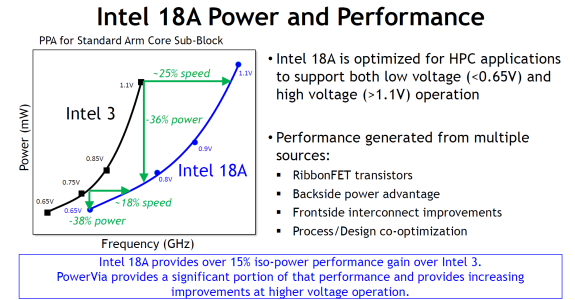

Intel themselves only claim 15%. Both on their literal IFS website, but on that slide that the graph comes from as well...Pat said that 20A should be got 15% PPW gain (v.s. Intel 3) and 18A should be got 10% (v.s. 20A).

Today, 18A boasts 25% PPW gain (v.s. Intel 3).

New nodes reduce TSMC's 60s gross marginsWhich is expected New Node Nowadays are very costly TSMC with all it's volume will take like 3-4 Years to reach the average.

Problem is that it's not just the U9 that's non existent, it's pretty much every PTL CPUalso U9 has always been a meme SKU in terms of volume at the start.

Could be BSPD too. We will have to see what 18A-P looks like. I'm assuming it's just Intel's usual issue of new nodes not clocking high.It's pretty clear that the cause for PTL's 5.1GHz max frequency is that the 18A process didn't meet the specifications of the PDK.

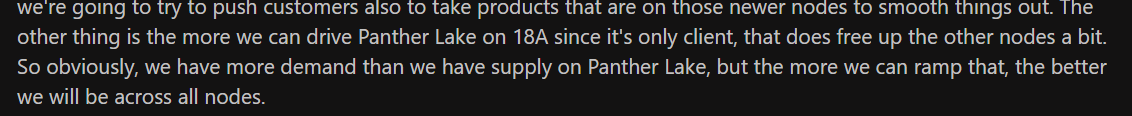

Yea, I think that's exactly what Intel said when they claimed they won't reach "industry standard" acceptable yields till late 26' or 27'.That reads to me as 18A is in what TSMC terms risk production, and won't reach what TSMC terms mass production until 2027.

This is exactly what I think the issue is. Never before has Intel outright been so blatant about admitting how dire the situation is. We didn't hear nearly as much talk about hurting margins or yields not being adequate for MTL for example.Intel admits yields are not fine or in corpo weasel language - "not where we would like them to be", so no - yields not fine.

This is exactly what I think the issue is. Never before has Intel outright been so blatant about admitting how dire the situation is. We didn't hear nearly as much talk about hurting margins or yields not being adequate for MTL for example.

some context from Patrick Moorhead:Following a conversation with Intel CEO Pat Gelsinger, analyst Patrick Moorhead reports that the company's Core Ultra 100 Meteor Lake CPUs could be facing production stress due to lower-than-expected yields. The issue is not expected to impact Lunar Lake and Alder Lake launch plans.

For the record, Pat G didn’t tell me that there were yield issues. This was *my* interpretation. But when your COGS are cited for a specific product are rising in a big, big way, with MTL, you *have* to surmise either yield or back end throughout (package) issues that can be very expensive.

Yea, I think that's exactly what Intel said when they claimed they won't reach "industry standard" acceptable yields till late 26' or 27'.

Also, what's interesting is in the q4 2025 earnings call, they kept on claiming that they were being hurt by the "early ramp" of 18A. This could mean they were early in the stages of 18A's ramp, but what I think meaning they ramped 18A "earlier" than what they would have liked considering where it is in node maturity.

The biggest issue for 18a thus far has been Fmax, not PPW.The 18a process was downgraded from the initial spec but not sure if it reverted all the way back to the initial 20a spec.

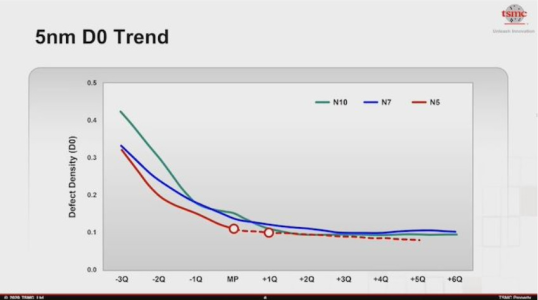

You can check the podcast here timestamp the issue is parametric.Yes I think the people touting the (unsourced AFAIK) claims that Intel's 18A D0 is 0.1 seem to be ignoring what Intel is actually saying. If 18A yields were already that good they would not be holding back on increasing production of 18A as they have stated they will be doing.

Even if they have sufficient quantity at this point of time it's going to take 2-3 Months for more laptops to show up(delivery+assembly) takes quite a bit of time.Problem is that it's not just the U9 that's non existent, it's pretty much every PTL CP

18AP will fix this tbh like Intel 3 did fix the Intel 4 having only 5.1 Ghz FmaxThe biggest issue for 18a thus far has been Fmax, not PPW.

I listened through the 18a section, didn’t hear anything about 0.1 D0 yields. . .You can check the podcast here timestamp the issue is parametric.

...the yields are adequate to address the supply, but they are not where we need them to be in order to drive the appropriate level of margins. By the end of next year, we’ll probably be in that space. Certainly the year after that, I think they’ll be in what would be kind of an industry-acceptable level on the yields...

...we’re going to be ramping the volume over the course of the next year. I wouldn’t say Intel 18A yields are in a bad place. They’re where we want them to be at this point. We had a goal for the end of the year, and they’re going to hit that goal. To be fully accretive in terms of the cost structure of Intel 18A, we need the yields to be better...

So then this is actual 20A then, just called 18A now, ie renamed???Intel themselves only claim 15%. Both on their literal IFS website, but on that slide that the graph comes from as well...

That can't be "just" parametric then.Clearly yields are a problem for 18A. They're bad enough that the process isn't profitable until late 2026 or 2027.

No idea, and frankly I don't think so.So then this is actual 20A then, just called 18A now, ie renamed???

He's been a shill for corporations for a whileView attachment 139593

The more I see Ian Cutress, the more he just sounds like an Intel spokesperson.

The most damning part was when he just complete bought into the Intel 20A spin hook line and sinker

View attachment 139595

I'm going to be a bit more optimistic and just assume he is very excited to get first hand information directly from those companies, and is naively believing them wholeheartedly, rather than outright selling out lmao.He's been a shill for corporations for a while

Lower tier stuff is more likely to get hurt by the ram crisis than the higher end stuff.If it was just a yield issue, wouldn't OEMs just get lower tier products? I imagine they would prefer that anyway due to ram costs.

I wonder how many wafers they are doing for PTL considering Intel is moving more tooling and yield are improvingLower tier stuff is more likely to get hurt by the ram crisis than the higher end stuff.

It's not just yield issue, as they have low total throughput as well, but even that might be attributed to the yield issue, if Intel is not willing to ramp up the node due to poor margins.

For reference, during the MTL low throughput ramp, they ran hot lots to pump out as much volume as possible.

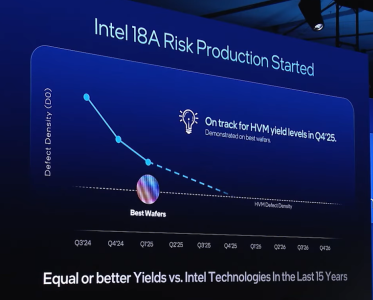

It's also a bit of a double whammy for Intel here, since Zinsner outright said that PTL ramp will help them move Intel 7 off of client and into server.

The biggest point is how much is demand for PTL cause OEM buy in Millions of UnitsIf it was just a yield issue, wouldn't OEMs just get lower tier products? They might not mind given RAM costs.

found the resource for 0.1 calculation it was a combination of these sorry for the confusionI listened through the 18a section, didn’t hear anything about 0.1 D0 yields. . .

there can be perf/watt improvement from the same lib through other optimizations like Intel 3 had vs 4No idea, and frankly I don't think so.

But ironically in PTL's case it doesn't actually matter much. Prob the most significant difference would have been the inclusion of denser libs on 18A vs 20A, which didn't even end up being used on the PTL compute tile lmao.

compare to other nodes for whome? IntelClearly yields are a problem for 18A. They're bad enough that the process isn't profitable until late 2026 or 2027. What's not clear to me is how that compares to other nodes.

will help them move Intel 7 off of client and into server.

OEM want cheap parts so either Raptor or whatever AMD hasAparently OEMs are adding Hawk and Rembrandt instead.

What does calculation mean exactly? IF TSMC had 0.05 instead of 0.1 in their graph, what value would "the calculation" produce for Intel 18A?found the resource for 0.1 calculation it was a combination of these sorry for the confusion