You don't know and we won't know until Intel does a Broadwell-like disclosure of xtor composition of their mobile die.

As if I don't read foundry papers.

Sorry to disappoint you, but Zen2 CCDs are even denser in heat@mm^2 and clock higher than ICL-U, too.

Hey, ICL-U ST ~= WHL-U ST.

That's, uh, something.

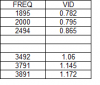

1) you are correct we don't know. All we know is the Ultra Performance Library is about the same density as the High Performance Library from TSMC.

2) If you read them, then why are you asking rhetorical questions when you know my answers?

3) You can't compare simply the processes across different fabs. AMD came from GF 14nm, not TSMC 16/12nm. That means we don't know the speeds they would have achieved with TSMC's process, nor if there would have been a regression on their nodes. We also saw AMD report that they moved up the TAGE branch predictor because they were getting LOWER speeds and needed IPC to compensate, at least until TSMC figured out a way to increase the clock speeds toward the end.

Intel, on the other hand, is having a regression from even the early 14nm Broadwell chips, needless to say the less dense iterations. As you mentioned, only the Ultra Performance library is as dense as the HPC libraries from TSMC, while the HP and other library from Intel are denser. In theory, if not in practice, that makes Intel's chip denser than AMD's. If it is not denser, then Intel is having MANY more problems, although I will note that Intel's information on density and libraries are NEVER anywhere close to what their CPUs have, save FPGA and one other product (I worked out that math months ago, but don't have it on hand, although I think it is in this thread).

But, your statement still doesn't address Intel's other issues, like removing 1 of the 2 dummy gates, using quad patterning or more for their chips, trying to integrate cobalt over active gate and cobalt in other places to counteract the electron bleed, etc. The 10nm node has been a poo show for Intel and EVERYONE knows that. So, considering it was TSMC figuring out how to get more speed at the 11th hour, and with all fabs agreeing that with these densities speed will be regressing (see the AMD server keynote discussing this from this past Spring or last fall, among others), there is no reason to think this isn't an aberration to the general trend, rather than the trend itself.

Not only that, uarch design can ALSO make it where it can not clock as high, rather than just process. Intel made major changes, going very wide on their cores in many respects. That is possible at smaller nodes. But, that doesn't mean those changes will not change the thermal properties of the cores once fabbed, which can effect the top frequency achieved.

4) AMDFan111 made so many statements that needed correction in that post, I just didn't even touch it. Seriously, not worth my time.

Hope that helps a bit.

Doesn't 7nm HPC have relaxed density compared to 7nm LP? I would assume ICL-U would be quite a denser than Zen2 CCDs.

It should be but isn't. 7nm HPC is roughly the density of Intel's 10nm Ultra Performance libraries on density. But Intel's density doesn't ever really approach their stated libraries density, whereas TSMC's products often are much closer to that theoretical value. But I point out other considerations on the topic in my response above this.

It is relaxed versus N7 mobile, but I dunno how is that relevant to hear density.

CCD is like, a 74mm^2 blob that radiates hellfire.

As I stated, see above. Also, evidently Intel's is a hot node too, otherwise it wouldn't be in the 3GHz range, it would be higher.