- Jun 10, 2004

- 14,607

- 6,094

- 136

Source:

https://www.anandtech.com/show/13535/intel-goes-for-48cores-cascade-ap

The good:

-Up to 48 cores per socket

-Aimed at 2S servers

-12 DDR4 channels

-Possible 5903 pin LGA socket

-Launch 1H2019?

The bad:

-14nm...

-UPI connection - no EMIB yet

-No mention of hyperthreading

-28-core XCC dies --> 24-cores "glued" together

The ugly:

-A current 24-core Xeon Platinum runs at 205W

-AMD launch of 7nm Epyc Rome imminent

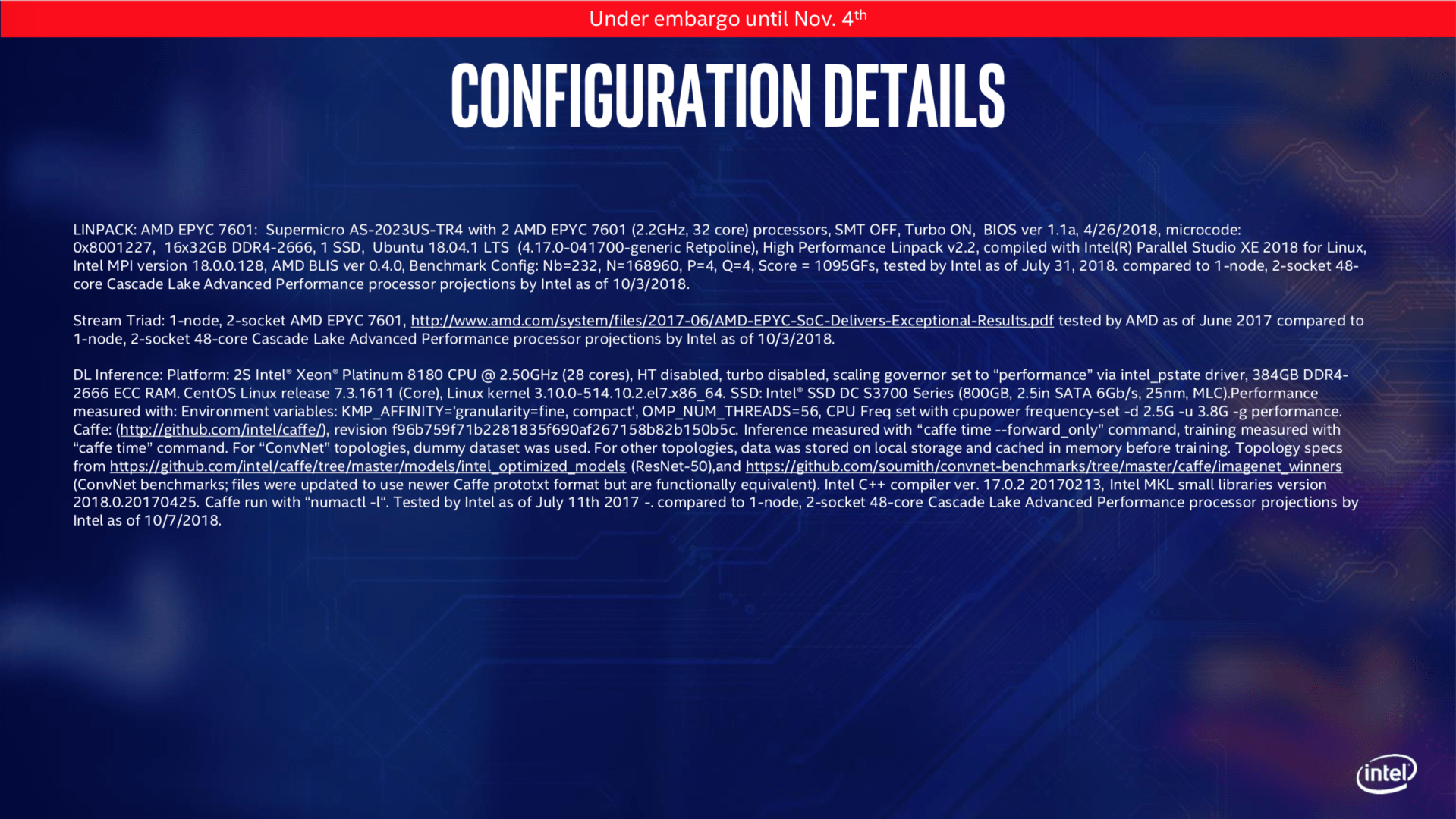

-They disabled SMT on Epyc for performance comparisons

https://www.anandtech.com/show/13535/intel-goes-for-48cores-cascade-ap

The good:

-Up to 48 cores per socket

-Aimed at 2S servers

-12 DDR4 channels

-Possible 5903 pin LGA socket

-Launch 1H2019?

The bad:

-14nm...

-UPI connection - no EMIB yet

-No mention of hyperthreading

-28-core XCC dies --> 24-cores "glued" together

The ugly:

-A current 24-core Xeon Platinum runs at 205W

-AMD launch of 7nm Epyc Rome imminent

-They disabled SMT on Epyc for performance comparisons