Covfefe

Member

- Jul 23, 2025

- 114

- 214

- 76

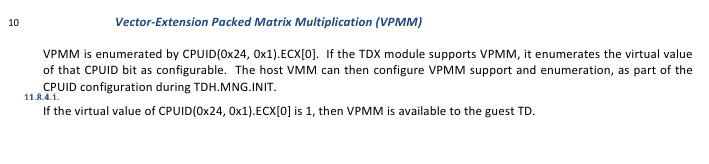

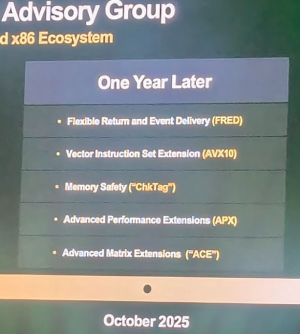

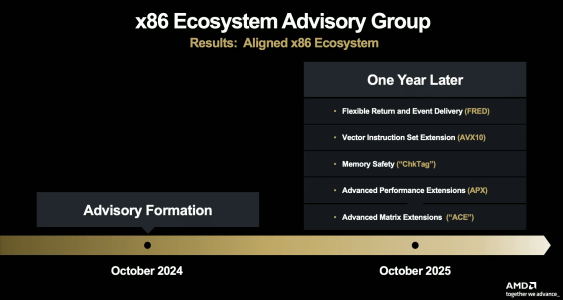

It's cool that the two rivals are working together to advance x86. Intel and AMD have adopted each other's new instructions in the past, but AFAIK they haven't worked together on new instructions. It's a unique situation, almost democratic.It looks like the group is alive and well and making noticable progress:

Advancing x86, Together

Advancing x86, Together Since its inception, the x86 Ecosystem Advisory Group (EAG) has been a driving force in shaping the future of x86 computing. Fueled by a deep – and somewhat unexpected – collaboration between AMD, Intel, and key industry partners, the group has made remarkable strides in aligwww.linkedin.com

There the AMD executive commented on the x86 EAG early successes:

It does look like future AMD processors will support FRED, APX and AVX10 (which is just glorified AVX-512 essentially) with more announcements to come (hopefully also from AMDs side)

I'm cautiously optimistic, but I could also see this falling apart in a few of different ways.

- AMD adds a new extension that Intel doesn't approve of. Intel releases their competing version, AMD leaves group. (Or vice versa)

- Leadership at one of the companies decide its bad business to help their competitor and leave the group.

- Progress on new extensions is bogged down by deliberation.

- Intel and AMD are pressured by industry partners into adding extensions that are beneficial in certain usecases but are bad for the overall x86 ecosystem.