Io Magnesso

Senior member

- Jun 12, 2025

- 578

- 164

- 71

I acceptOnly when you count the fact that LNC has large core private caches.

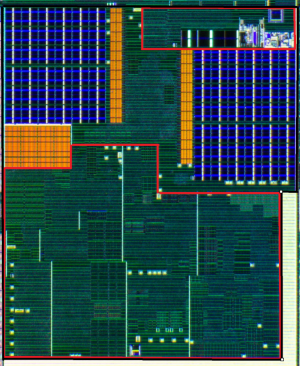

What really saves Apple a bunch of area is their caching hierarchy.

A LNC core without the L1.5 + L2 SRAM arrays and associated logic related to handling that is similar in area to the M3.

Meanwhile Xiaomi's X925 implementation with the core private caches is still smaller than the M4 P-core.

The M4 P-core is massive.

But the E-cores aren't on NVL for ST performance though.

Why would Intel want the E-cores to be so much larger on NVL, when the entire point of them being on there is nT perf/watt?

LNC is the worst P-core by any of the major vendors, I agree, but LNC is only that large because of them being stuffed with massive core private caches.

The problem is that you don't necessarily need caches that big to have similar Zen 5 perf. Willow Cove for example had a 2.5x increase in L2 cache capacity over SNC, IPC didn't change much, actually regressed in TGL vs ICL. RPC increased L2 cache by 60%, and RPL IPC is low single digits better than GLC IPC. From Chips and Cheese's article about arm chair QBing GLC, we see in simulations that using AMD's L2 cache, which cuts L2 capacity nearly in third vs GLC, results in only <3% IPC losses.

Intel's huge core private caches seem to be there for energy efficiency and isolating them from the terrible uncore, both in server and in client. From a perf perspective, they can prob reduce caches to a large degree and still retain most of the perf, if area was that much of a concern for them. Or, if their uncore was just better.

Looking at just the core logic + L1, Zen 5 doesn't seem to hold on to the AMD area lead they used to have. I think LNC dramatically improved Intel's area competitiveness. Though this also might just also be because LNC cut away AVX-512...

LNC is

Is the difference between PPW true?We will see. You must understand why at the very least, if that is the case, it would be surprising.

The ratio has been getting worse, but you can still roughly equate a P-core to an E-core cluster, which is where the 1:4 ratio is coming from.

Where has been this rumored? I've not heard of it tbh.

If the area increase is that drastic, sure, than Arctic Wolf can have such a large IPC improvement.

Never heard of anyone saying it would be that large though.

For a lack of trying.

That's not the point, the point is that getting to 256 bit width to support AVX-512 will be a substantial area cost.

I think people overhype the E-cores too much.

It's great in area. But in power and perf, arguably the more important two categories, it's okish.

They could be sacrificing a bunch of power and perf to chase after area, but that's the way things are.

Sure, that's fine.

A massive difference....

Intel is also done with this. Hence why they are using N2 over 18A-P for NVL-S lol. Power on announced in the earnings call this week hopefully.

The best comparison should be NVL 4+8 tiles vs NVL 8+16 tiles.