Timur Born

Senior member

Hello.

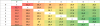

Looking at both Anandtech's 13900K and 12900K review and my own core-to-core latency tests demonstrates that instead of ring or mesh like latencies there is a star like concentration of lower latencies around one physical core. Transfers from and to that core and its directly surrounding cores is faster, as if all load goes through that core first and then to the final destination core. And while one direction is slightly faster than the other the faster core-to-core connections are still faster even the other way around.

For Anandtech's 13900K sample this was physical core 2, on their 12900K sample it was core 5, on my own 13900K it is either core 6 or maybe 7 (they are very close). The 12900K review states "In our core-to-core latency test which showcases the physical topology of the chip", unfortunately there are no further details.

On a ring I would expect neighboring cores to always have lower latencies than further away cores. On a mesh I would expect interconnections between specific cores (like opposite of the ring) to be faster. But here I we see one specific core being the nexus of all transfers. Can someone explain this further?

This has practical implications. My own CPU uses cores 2+3 as highest clocking (58x) cores at stock. But going by core-to-core latencies and their equal quality in stability and temps it seems better to use cores 6+7 as highest clocking cores instead.

Looking at both Anandtech's 13900K and 12900K review and my own core-to-core latency tests demonstrates that instead of ring or mesh like latencies there is a star like concentration of lower latencies around one physical core. Transfers from and to that core and its directly surrounding cores is faster, as if all load goes through that core first and then to the final destination core. And while one direction is slightly faster than the other the faster core-to-core connections are still faster even the other way around.

For Anandtech's 13900K sample this was physical core 2, on their 12900K sample it was core 5, on my own 13900K it is either core 6 or maybe 7 (they are very close). The 12900K review states "In our core-to-core latency test which showcases the physical topology of the chip", unfortunately there are no further details.

On a ring I would expect neighboring cores to always have lower latencies than further away cores. On a mesh I would expect interconnections between specific cores (like opposite of the ring) to be faster. But here I we see one specific core being the nexus of all transfers. Can someone explain this further?

This has practical implications. My own CPU uses cores 2+3 as highest clocking (58x) cores at stock. But going by core-to-core latencies and their equal quality in stability and temps it seems better to use cores 6+7 as highest clocking cores instead.