I just read the article...

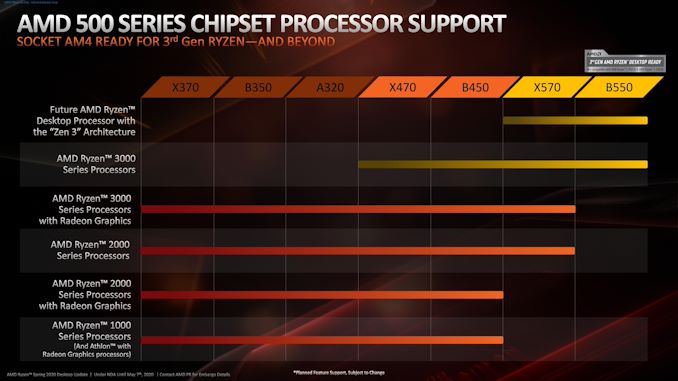

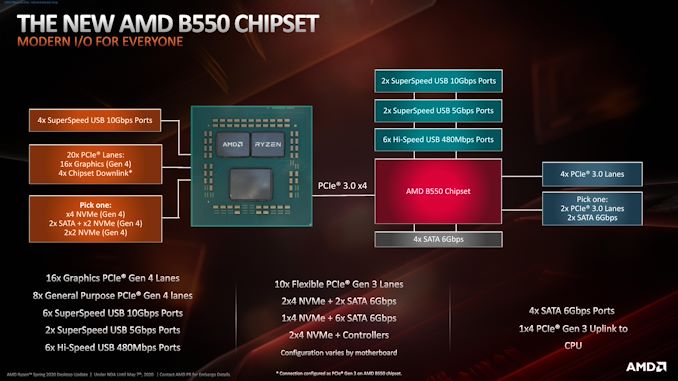

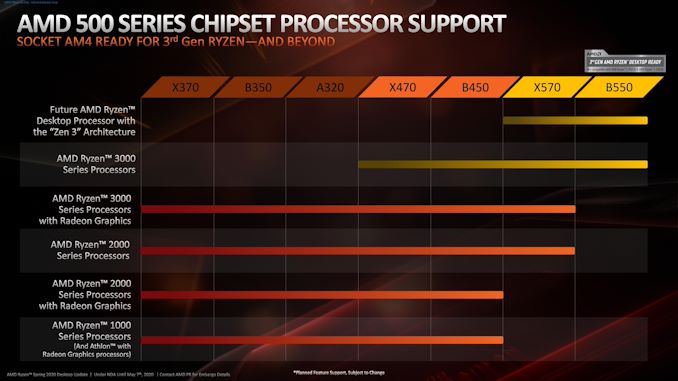

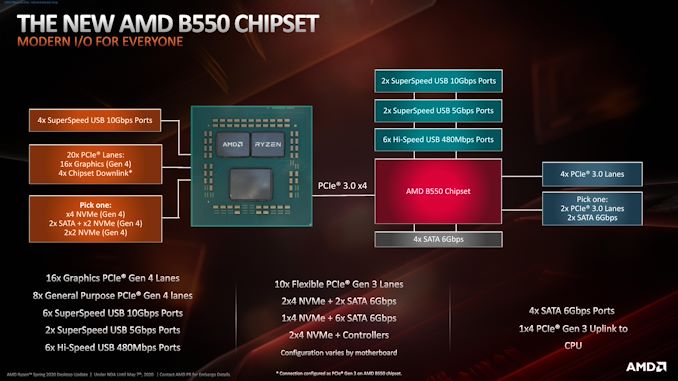

So let me get this straight, this chipset is coming out like a year later, they did not even bother to add CPU PCI-E 4.0 uplink support or to increase the number of sata ports that is ALREADY a problem on every 6 sata B450 motherboard (NVME x4 disables the 2 SOC Sata, thus 6 sata B450 mbs losses 2 sata if NVME is used), and they even dare to futher reduce backguard compatibility?

I was not expecting for the PCI-E lanes FROM the chipset to be 4.0, but only USB 3.2 G2, no more satas, CPU link still 3.0 and the PCI-E lanes 3.0 is beyond disappointing.

So let me get this straight, this chipset is coming out like a year later, they did not even bother to add CPU PCI-E 4.0 uplink support or to increase the number of sata ports that is ALREADY a problem on every 6 sata B450 motherboard (NVME x4 disables the 2 SOC Sata, thus 6 sata B450 mbs losses 2 sata if NVME is used), and they even dare to futher reduce backguard compatibility?

I was not expecting for the PCI-E lanes FROM the chipset to be 4.0, but only USB 3.2 G2, no more satas, CPU link still 3.0 and the PCI-E lanes 3.0 is beyond disappointing.

Last edited: