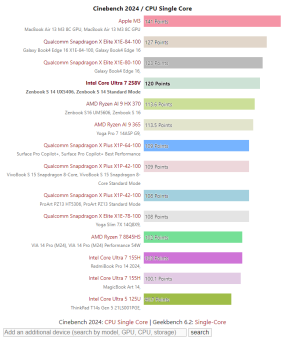

Barring one exception (Apple) it seems the x86/ARM SoCs end up pretty similar to each other overall.

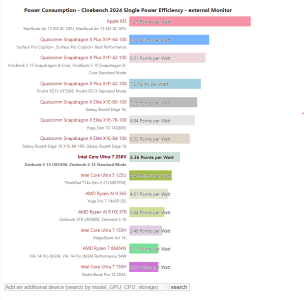

There is a notable advantage on 1T power draw for Qualcomm. But in MT that disappears when even more "terribly inefficient" x86 decoders are active, with SMT (Strix) or without SMT (LNL). So how much of that 1T efficiency advantage is due to their mobile phone expertise and power efficient cache hierarchy rather than ISA? I have no way of knowing but that the efficiency advantage disappears in MT suggests it isn't the ISA itself at fault but something else.

There is a notable advantage on 1T power draw for Qualcomm. But in MT that disappears when even more "terribly inefficient" x86 decoders are active, with SMT (Strix) or without SMT (LNL). So how much of that 1T efficiency advantage is due to their mobile phone expertise and power efficient cache hierarchy rather than ISA? I have no way of knowing but that the efficiency advantage disappears in MT suggests it isn't the ISA itself at fault but something else.