What is Voyager?

Also it's not an RDNA clone, it IS RDNA - they just designed it for TSMC nodes so it performed less than ideally on Samsung's, and they will have to start from scratch again with the 3nm GAA node.

Voyager/Angle is the licensed IP name once it goes in the product (Xclipse is the market name). Samsung re-stated agreement with AMD allows them to do more than just re-spin AMD's design. So, it is more like Hygon's Dhyana now.

Next GPUs found/leaked/etc:

Magellan

Titan

Ariel

You immediately send the goalposts flying to "welllll, they're derived from Andes RISC and won't go into the RVA profile."

You are the one moving the goal post of a custom instruction. Basically, come Q2'24 they can drop the P-ext.

The current maintainer for P extension is NOT Andes, by the way. It is basically starting from scratch again with Berkley UC handling it. As the vector crypto extensions utilizes the P-ext opspace.

https://github.com/riscv/riscv-opcodes/issues/146#issuecomment-1362708942

"Vendors claiming support for "P" are claiming support for something that isn't a RISC-V standard. So it isn't really relevant."

In this case, with the P ext: Fractional LMUL/SEW in V-ext can be used to do P-ext.

128-bit Unit/VLEN=128 => mf2/111 # LMUL=1/2 and 000 # SEW=8 is equivalent to an 8-bit*8 Packed op.

Custom instructions will not be used by software in the general market. Any custom instructions will not be used anywhere (generic-image). Stop moving the goal post that never existed. RVA is the only standard being supported for Datacenters/Desktops/Laptops. Unless for example, Qualcomm/Rivos accept the maintainership of RVH "High Performance" profile. However, it is unlikely they will actually do that.

Andes purpose of P-ext is to make RISC-V DSP compatible with AndeStar V3. Every AndeStar RISCV custom instruction is to make it compatible with AndesStar V1/V3. No one is going to use Andes custom instructions in their products. As it IS not mandated to use them, only RVM23 has P-ext.

Andes RISC-V Performance custom ISA = AndeStar V3 Performance [V1+V2] ISA // Which is replaced by Bitmanips

Andes RISC-V CoDense custom ISA = AndeStar V3 Density (Mixed-length) ISA // Which is replaced by Compressed

etc.

The extensions used by software in the general market (Android/Tizen/Windows/ChromeOS/FuschiaOS/Linux) will be the standard ones. Which will not be Qualcomm custom, Andes custom, somecompany custom instruction set.

"For some deep embedded markets, highly customized processor configurations are desirable for efficiency, and all software is compiled, ported, and/or developed in-house by the same organization for that specific processor configuration. However, for other markets that expect a substantial fraction of software to be delivered to end-customers in binary form, compatibility across multiple implementations from different RISC-V vendors is required.

...

The primary goal of the RVA profiles is to align processor vendors targeting binary software markets, so software can rely on the existence of a certain set of ISA features in a particular generation of RISC-V implementations." - RVA Profile overview

For example: No one in the general market has used RISC-V Turbo/"XIE (XuanTie Instruction Extension)" for T-head's C910. Even though it actually has purchasable products: TH1520 and SG2042. These products are only running RV64GC/RVA20, not even the RVV 0.7.1 custom instruction set is being used.

On progress with RISC-V: there is only one instruction preventing Server RISC-V and it is a instruction tied to AutoFDO:

"RISC-V ISA extension (proposal) to allow recording of control transfer history to on-chip registers, to support usages associated with profiling and debug."

After which, this is done:

https://wiki.riseproject.dev/display/HOME/SE_01_022+-+RISC-V+Server+SoC+Referece+Board

RISC-V will be everywhere.

"RISE Optimization Manual" :: target hardware: smartphone, laptop, desktop, server; OoO; rv64gv*

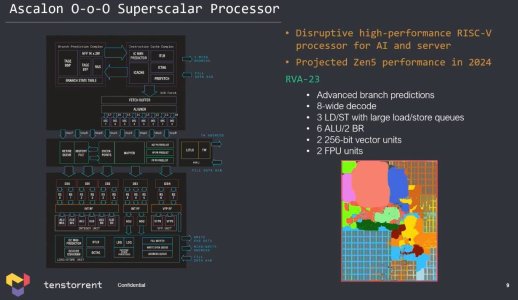

Ventana/Tenstorrent are server first. AMD is on RISE, with AMD Strategic Silicon Solutions being involved.

Bare minimum is Oasis going forward. Everything will speed up with hardware (esp. closer to Spec Target) becoming available.

Ventana's/Imagination's Veyron V2+Imgtec DXD APU is likely to be available after October 22-23, 2024

Vulkan 1.3, OpenGL 4.6 via Zink, OpenGL ES 3.2, Open CL 3.0, DirectX 11_0 FL, (DirectX 12_2 over time with VKD3D).