No, his explanation would amount to higher power comsumption at a same frequency, while what i m explaining require the same power comsumption at a given frequency, that s all the difference.

You have some knowledge, undoubtly, but you dont understand what it is about here, that s because you think that a switching transistor is not an analog component, hence your flawed assumptions and insistance because you dont understand the matter.

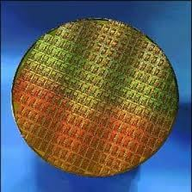

For the time all you need to know is that for finfets, contrary to planar transistors, the limiting factor for speed is the miller effect (not the current capability) within the transistors, that s documented, and what i m talking about is how to neuter this effect.

In Chaucer’s Canterbury Tales, the second of the tales told by the pilgrims is The Miller’s Tale. Since this is a family blog, I’ll leave you to research the tale yourself. But FinFETs hide another Miller’s Tale, due to Miller capacitance, sometimes called the Miller effect. This is significant...

semiwiki.com

Is that good enough to help you understand.?..You could have googled the thing and got out of your erroneous insistance and non sense.