- Mar 27, 2009

- 12,968

- 221

- 106

So far:

Intel 660p---> http://www.tomshardware.com/news/intel-760p-660p-700p-specifications,36335.html

Intel 660p---> http://www.tomshardware.com/news/intel-760p-660p-700p-specifications,36335.html

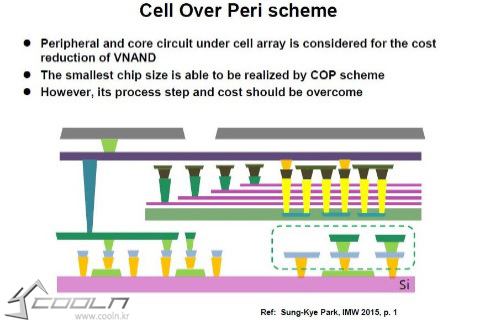

Last but not least is the most interesting leak: In the middle of the chart is the Intel SSD 660p with 4-bit per cell (QLC) flash. The SSD 660p listing shows three capacities (512GB, 1TB and 2TB). The performance is much higher than we expected to see from QLC at right out of the gate. The leak says the 660p will achieve up to 1,800 MB/s sequential read and 1,100 sequential write speeds. The random performance clocks in at 150,000 IOPS for both reads and writes.

QLC was a hot topic at CES last week, but only behind closed doors. No one wanted to go on the record, but we know IMFT (Intel Micron Flash Technology) has it ready for the most part. Companies are excited about the cost-cutting technology but need controllers to pair with it. One source told us to expect 512GB QLC SSDs for around $100.