- Mar 10, 2006

- 11,715

- 2,012

- 126

From the IEDM 2016 program

So HD SRAM cell size on TSMC 7nm is 0.027um^2, roughly a 2.6x shrink from 16FF+ (0.07um^2).

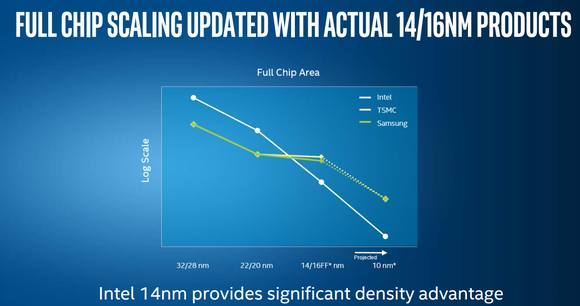

Intel needs to shrink its 10nm process by a factor of 0.53x or better to maintain density leadership. But it does look like TSMC 7nm ~= Intel 10nm in terms of density.

A 7nm CMOS Platform Technology Featuring 4th Generation FinFET Transistors with a 0.027um2 High Density 6-T SRAM cell for Mobile SoC Applications (Late News)

So HD SRAM cell size on TSMC 7nm is 0.027um^2, roughly a 2.6x shrink from 16FF+ (0.07um^2).

Intel needs to shrink its 10nm process by a factor of 0.53x or better to maintain density leadership. But it does look like TSMC 7nm ~= Intel 10nm in terms of density.