https://www.servethehome.com/amd-epyc-rome-details-trickle-out-64-cores-128-threads-per-socket/

New AMD EPYC Rome Generation Disclosures

The next generation of AMD EPYC 7000 series is shaping up to be a Xeon killer. The next-generation AMD EPYC 7000 series is codenamed “Rome” and it is going to be a big deal. Instead of adopting Zen+ like the desktop Ryzen CPUs, the new EPYC generation will use the Zen 2 architecture which means improved IPC gains from two generations of core tweaks. Beyond the IPC gains, the next generation parts will be based on 7nm production.

The impact of leapfrogging Intel and using 7nm is several-fold. First, Rome will have up to 64 cores and 128 threads in a single socket. The new CPUs will be socket compatible with the current SP3 socket motherboards with a small caveat. At STH, we expect Rome to adopt PCIe Gen 4 so motherboards will have to support the higher signaling rates to achieve PCIe Gen 4. We also expect the next generation to have greatly improved Infinity Fabric, an area that the first generation product has room to improve upon.

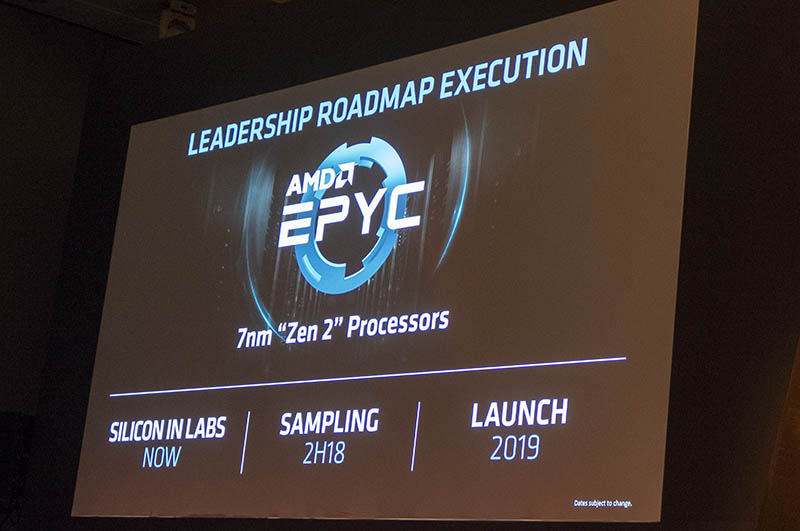

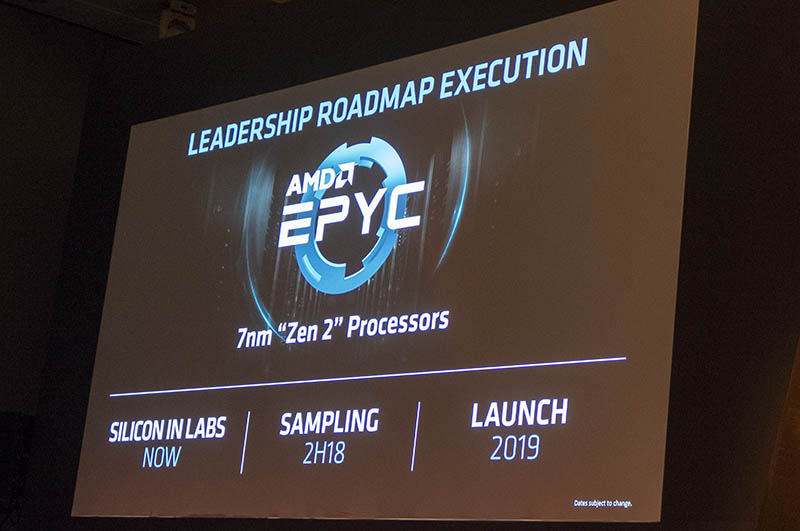

The other key disclosure is that AMD already has silicon in their labs with the next generation AMD EPYC Rome CPUs in their labs. They will be sampling to partners in the second half of 2018 and will launch in 2019.

This is going to put a lot of pressure on Intel Xeon as Cascade Lake is not going to come anywhere close to the core count of AMD EPYC’s next generation. Intel is scrambling to build a competitive response. 2019 is going to be extremely interesting in the server market.

New AMD EPYC Rome Generation Disclosures

The next generation of AMD EPYC 7000 series is shaping up to be a Xeon killer. The next-generation AMD EPYC 7000 series is codenamed “Rome” and it is going to be a big deal. Instead of adopting Zen+ like the desktop Ryzen CPUs, the new EPYC generation will use the Zen 2 architecture which means improved IPC gains from two generations of core tweaks. Beyond the IPC gains, the next generation parts will be based on 7nm production.

The impact of leapfrogging Intel and using 7nm is several-fold. First, Rome will have up to 64 cores and 128 threads in a single socket. The new CPUs will be socket compatible with the current SP3 socket motherboards with a small caveat. At STH, we expect Rome to adopt PCIe Gen 4 so motherboards will have to support the higher signaling rates to achieve PCIe Gen 4. We also expect the next generation to have greatly improved Infinity Fabric, an area that the first generation product has room to improve upon.

The other key disclosure is that AMD already has silicon in their labs with the next generation AMD EPYC Rome CPUs in their labs. They will be sampling to partners in the second half of 2018 and will launch in 2019.

This is going to put a lot of pressure on Intel Xeon as Cascade Lake is not going to come anywhere close to the core count of AMD EPYC’s next generation. Intel is scrambling to build a competitive response. 2019 is going to be extremely interesting in the server market.