- May 11, 2008

- 23,225

- 1,565

- 126

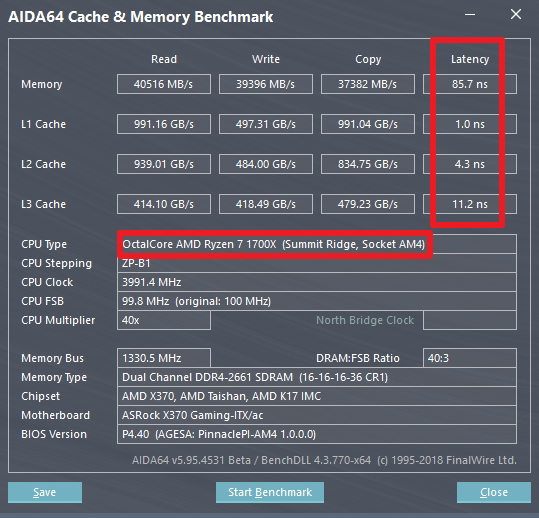

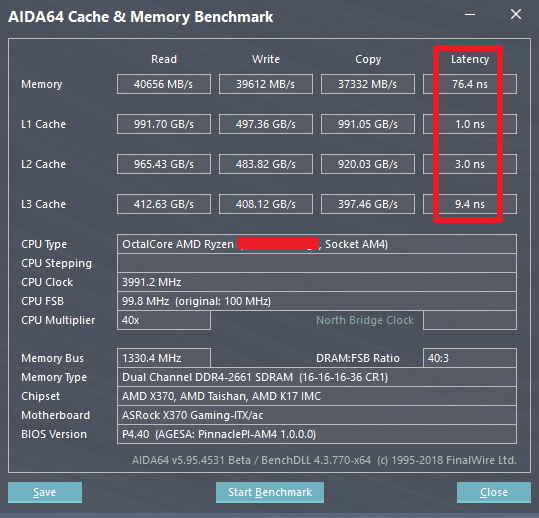

With the original zen we noticed the inter ccx communication is limited to the IF which in turn is coupled to ram speed.

Assuming the IF between the CCX is optimized a bit but not for example doubled in bandwidth and it is still coupled to memory speed, one wants high memory speeds. Now since the JEDEC specification for DDR4 now also officialy supports 3200MHz speeds (albeit at 20 or 22 clocks for memory timings) this is doable.

We noticed in the past that inter thread communications suffered from the IF bandwidth between the CCX. Sometimes affecting games and other programs that have high inter thread communication.

It would be nice if AMD has been able to double IF bandwidth between the CCX, IF is scalable so perhaps it is also scalable between the CCX. But this remains to be seen.

My question is, even with memory timings of :

CAS Latency (CL) 20

RAS-to-CAS-Delay (tRCD) 20

RAS-Precharge-Time (tRP) 20

Row-Active-Time (tRAS) 40

at 3200MHz, the IF would be much faster and inter CCX communication would benefit.

What is worse for ryzen, high memory timings at high speeds (3200MHz or higher) but with higher IF bandwidth or low speeds (2933MHz or less) at low memory timings but with lower IF bandwidth ?

Common sense says that the inter CCX communication must be as fast as possible.

High memory latency is offset by caches and smart prefetching / speculative loading of data into the cache.

Assuming the IF between the CCX is optimized a bit but not for example doubled in bandwidth and it is still coupled to memory speed, one wants high memory speeds. Now since the JEDEC specification for DDR4 now also officialy supports 3200MHz speeds (albeit at 20 or 22 clocks for memory timings) this is doable.

We noticed in the past that inter thread communications suffered from the IF bandwidth between the CCX. Sometimes affecting games and other programs that have high inter thread communication.

It would be nice if AMD has been able to double IF bandwidth between the CCX, IF is scalable so perhaps it is also scalable between the CCX. But this remains to be seen.

My question is, even with memory timings of :

CAS Latency (CL) 20

RAS-to-CAS-Delay (tRCD) 20

RAS-Precharge-Time (tRP) 20

Row-Active-Time (tRAS) 40

at 3200MHz, the IF would be much faster and inter CCX communication would benefit.

What is worse for ryzen, high memory timings at high speeds (3200MHz or higher) but with higher IF bandwidth or low speeds (2933MHz or less) at low memory timings but with lower IF bandwidth ?

Common sense says that the inter CCX communication must be as fast as possible.

High memory latency is offset by caches and smart prefetching / speculative loading of data into the cache.