http://www.bitsandchips.it/52-english-news/6816-rumor-tsmc-will-produce-the-huge-gp100-interposer

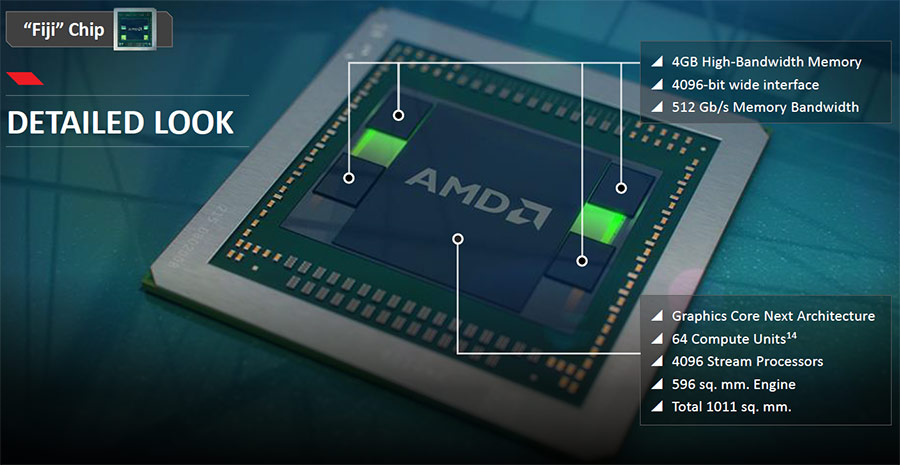

"According to our source, TSMC is sampling the Interposer for the next GP100 NVIDIA GPUs and it will be huge! We talking about a 1200 mm2 interposer (Fiji interposer is about 1000 mm2)."

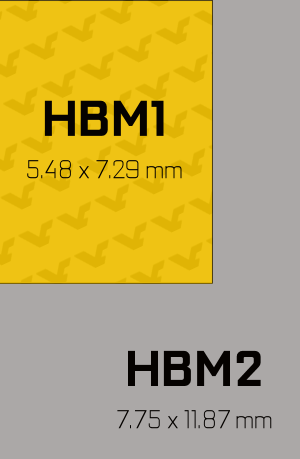

So will Nvidia and TSMC be able to get such a complex big die GPU on a massive interposer right the first time around. Nvidia has no experience with HBM2 and 2.5D stacking. TSMC has experience as they have developed FPGAs with Xilinx which utilize interposers.

http://www.ispd.cc/slides/2013/0_madden.pdf

The interposer size is even bigger than Fiji's. Well Nvidia seems to be going all out with GP100 to defend its HPC turf from Intel Knights Landing.

"According to our source, TSMC is sampling the Interposer for the next GP100 NVIDIA GPUs and it will be huge! We talking about a 1200 mm2 interposer (Fiji interposer is about 1000 mm2)."

So will Nvidia and TSMC be able to get such a complex big die GPU on a massive interposer right the first time around. Nvidia has no experience with HBM2 and 2.5D stacking. TSMC has experience as they have developed FPGAs with Xilinx which utilize interposers.

http://www.ispd.cc/slides/2013/0_madden.pdf

The interposer size is even bigger than Fiji's. Well Nvidia seems to be going all out with GP100 to defend its HPC turf from Intel Knights Landing.