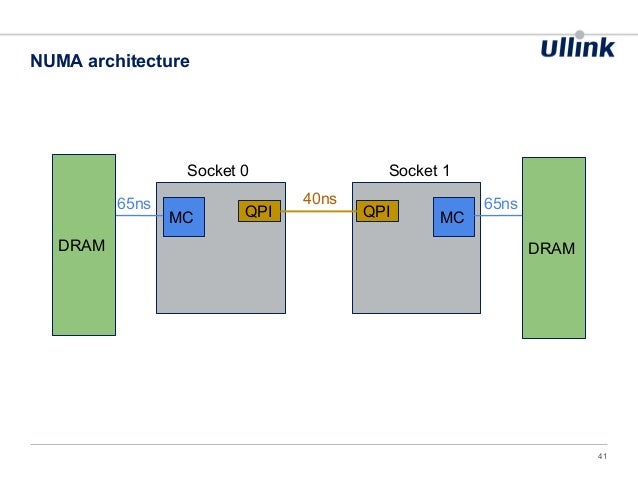

Kind of makes me wonder how well XMR mining goes on a TR2 CPU, with the added latency for two of the cores. Then again, it primarily exercises the L3 cache, so with two more active dies, I assume that it will have twice the total L3 cache of the original TR CPUs. Which, it was mentioned, could pay for themselves within a year mining XMR in the background. Let's see if TR2 can pay for itself.

I'm pretty excited. I already (just) bought the 2700X and an Asus X470 Prime Pro ATX board (Newegg combo, $55 off), and a nice DIYPC Vanguard tempered-glass case with 4x RGB fans and a fan / lighting controller built-in. QC and longevity may not be the best, but it has a LOT of nice features in a case. This may be DIYPC's best case yet. It was on sale for $89 with a $10 MIR, which I probably won't bother to send in.

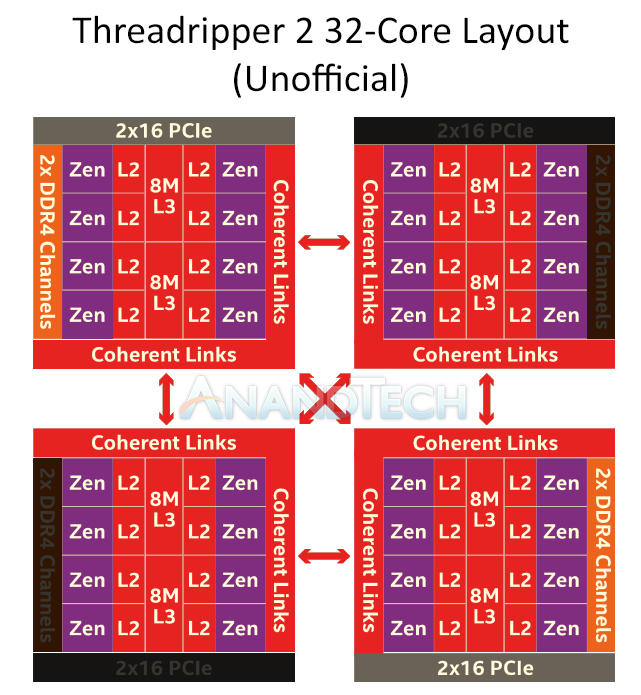

But even though this is my first 8C/16T CPU, I'm salivating at the idea of a 32C/64T machine. Crazy good!

Oh yeah, the 2700X is finally going to get 32GB of RAM. My R5 1600 rigs with dual RX 470/570 GPUs, mining on all three (2x GPU and 1x CPU), take up enough virtual memory, that opening maybe 100-200 tabs in Firefox Nightly pushes me over the limit of 16GB of physical RAM.