- Mar 27, 2009

- 12,968

- 221

- 106

Looking at number of P/E cycles the MX500 and the 545s however; then they are both specced for 1500 P/E cycles.

Difference in Wear Level factor?

Difference in Write Amplification factor?

Looking at number of P/E cycles the MX500 and the 545s however; then they are both specced for 1500 P/E cycles.

Difference in Wear Level factor?

Difference in Write Amplification factor?

upgraded error correction and end to end data path protection it offers

What is confusing to me is that despite the Intel 545s having more ECC (via SM2259) it has the same P/E rating as the MX500.

This implies the Intel SSD would be using lesser grade IMFT NAND and making up for it with a better controller.

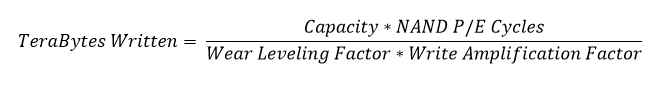

I thought that the P/E rating was wholly dependent on the NAND grade / technology / process, and not the controller? The TBW of a drive, being a factor of the P/E, the controller, ecc, and NAND grade altogether, including firmware tweaks to one mfg's drive over another? (For example, slowing writes down in "enterprise" versions of drives, to enhance endurance.)

ilicon Motion's internal testing with a 120-degree bake to accelerate the degradation process shows a 3x endurance increase.

The end result is that SSD vendors can use lower-cost, lower-endurance flash and still guarantee the same number of writes per day that we have now.

Difference in Wear Level factor?

Difference in Write Amplification factor?