Area matters less now, since you can always just suffer worse margins if you have too but still create a competitive CPU. If you suck in perf or power, you just to eat it esentially.Area matters more than ever now, given each mm^2 yielded costs more each node.

Before chiplets, Intel couldn't compete add cores no matter how hard they tried, with ICL and other 14nm parts being only marginally less than reticle limit. They were what, north of 600mm2?

Intel rn spends more die area on GNR than Turin classic, but they are still able to match core counts on products built from a close-ish nodes (5nm class stuff)

Why would apple bother using it atp? They can easily afford to use whatever they want.It's standard Mx Max stuff and it sucks.

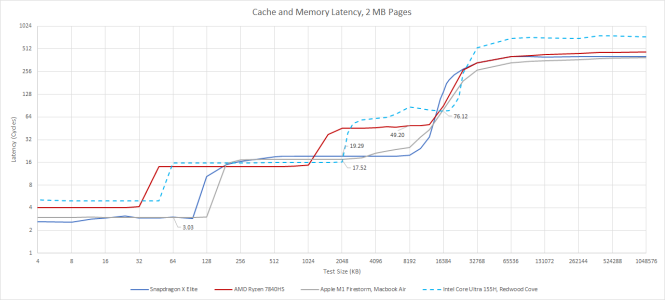

The L2 of these systems are pretty close to the latency in cycles as what you see in Intel, ARM, and AMD CPUs.not how it works.

Toddler caches can't handle workloads that spill into L2 (which in server is ~most of them). Infinite L2 trashing especially on i$ side, just what everyone wanted.

The lack of a L3 is where the large gap appears to be (if you added desktop systems with their full L3 configs to this chart) not the L2.

If you are a startup, why would you use a cache hierarchy that has little chance of working well? It's not as if what ARM, Intel, and AMD are doing is the "new" method of cache hierarchies...meme lolcow startups that shipped 0 parts ever do not count. they don't even have human rights as far as server multiprocessors are concerned.

This was what, almost 2 decades ago?The main limitation is going back to Dunnington (or Woodcrest if you're really into having no real LLC) sucks.

If Intel is willing to spend a bunch of die area on something as niche as AMX, why wouldn't they on something much more important in per-core perf?Who cares about Intel, they're completely irrelevant in server.