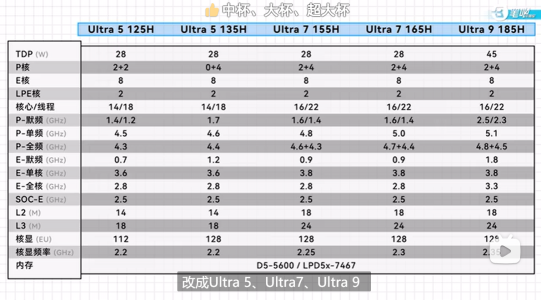

What I had seen is that the current LNL is 170 mm2 on N3B plus the IO die @ 46 mm2 plus some glue chip that looks to be about 20 mm2.

There is no official number on die size on Lunar Lake from Intel, only some extimates on Twitter of 140mm2 N3 + 46mm2 N6. The third thing in the corner that looks like another die is just a filler.

AMD's Strix Point has a much bigger monolithic die size of 233 mm2, but also has a much less complex packaging. Also, Strix Point has 12 cores (with SMT) vs the 8 of LNL without.

Lunar Lake cost is probably close to 12 core Strix Point, but they are addressing different market.

I went on line and found most of the Laptops with Strix Point in the highest end gaming laptops, most including NVidia GPU (in $2,000+ range), very few on the market without dGPU, in Lunar Lake price range. One possibility is that most of the iGPU only Strix Point were sold out.

It's still just days from Lunar Lake launch and the new models are still trickling in.

To me, LNL using Intel's shiny new architecture on the best TSMC process node possible is still going to have its hands full with AMD's Zen 5 lineup in the laptop market in general, but LNL does look like a pretty promising CPU for thin and light.

Yeah, different segments between Strix Point, Lunar Lake and upcoming Kraken.

Strix Point - high end and gaming

Lunar Lake - premium thin and linght

Kraken - mainstream pricing segment, with CoPilot branding (if anyone cares)

This whole "get rid of SMT" thing might work OK in a laptop, but I am wondering how this is going to play out in the high end data center. AMD's SMT gains them about 25% per core in threaded application execution. I suspect that having SMT in Zen 5c in a 192 core configuration in Turin AND having a more efficient process node @ N3E (vs N4P), Skymont cores might not feel so efficient in comparison any more..... but I could be wrong. I am just curious as to how this whole "no SMT" thing is going to work out for Intel.

I think for Lunar Lake, no SMT is no problem. It was probably a good decision by Intel for target market of Lunar Lake, if it, even marginally contributed to better ST, smaller die, better efficiency.

I don't think Sierra Forrest will be very competitive vs. Turin Dense either with SMT on or off (on Turin), but Clearwater Forrest with Skymont cores may be a different story. Likely clearly superior vs. Turin Dense with SMT off.